반도체 소자 소개 finfet

fin형태의 구조를 가졌으며 기존 planar fet와 달리 gate3개의 면이 채널을 형성하는 구조입니다.

finfet장점

gate가 3개의 면에 있기 때문에 채널에 대한 게이트 장악력이 증가합니다. short channel effect가 감소합니다. 미세화에 유리합니다

finfet단점

높은 공정 비용이 드는 단점이 있습니다. fin폭 fin높이의 변화에 따라 ion, loff variability문제가 생깁니다. 열방출 문제가 있고, 소자의 크기가 작아질수록 열방출하는 길이 좁아집니다.

finfet발전

크기가 작아지면서 생기는 누설전류와 vt를 둘 다 잡기 위해서 게이트 산화막의 두께를 줄였습니다. 산화막의 두께가 줄어들수록 게이트의 채널 영향력이 더 커지기 때문에 short channel effect를 효과적으로 극복할 수 있습니다. 그러나 게이트 산화막의 두께를 계속 줄인다고 해도 채널과 떨어진 곳은 조절이 불가능했습니다. body쪽으로 누설전류가 흐르는 것들은 막을 수 없었습니다. 그래서 body에 oxide절연체층을 만들어서 leakage current를 조절하였습니다.

2gate가 channel조절이 쉽다는 것을 알고, double gate를 시도합니다. double gate로 만들면 channel 조절이 쉽다는 걸 알게 되었습니다. 맨 처음 type1으로 도전을 하게 됩니다. 그러나 공정이 어려워서 포기를 합니다. type2와3로 발전하게 되었고 type2는 공정이 type3보다 어려워서 type3가 마지막에 살아남게 됩니다.

그래서 전체적인 발전 과정을 보면 그림과 같습니다. bulk planar, finfet, tri-gate, pi-gate, gaa

gaafet구조에서 mbcfet구조로 변경하게 됩니다. gaafet구조보다 mbcfet구조가 전류가 더 많이 흐를수 있고, 넓이 조절을 통해서 성능을 자유롭게 조절할 수 있기 때문입니다.

삼성에서 3nm부터 mbcfet구조를 활용하고 있습니다. TSMC는 3nm까지는 finfet구조를 사용하고 2nm부터 gaa구조로 진입할 예정입니다.

corner effect

finfet의 fin을 직사각형으로 만들면, 모서리 부분이 벽에 비해 큰 electric field가 가해집니다. 모서리 부분은 channel이 더 빠르게 형성됩니다. 빠르게 형성된 channel이 leakage current가 되어서 성능을 떨어뜨립니다. 또한, 모서리 쪽이 다른 곳 보다 온도가 올라갑니다.

coner effect 해결 방법

1. 모서리 깍기

2. 핀은 삼각형 모양으로 만들기

3. sin을 씌워주기

finfet을 만들기 위한 photolithography공정

photo mask에 그려진 pattern을 wafer에 옮기는 과정입니다. mask는 wafer에 설게할 pattern이 그려진 판입니다. 빛은 감광제의 화학반응을 일으키는 역할을 합니다. pr은 빛과 반응을 통해 선택적 현상을 가능하게 합니다. photolithography에는 총 8개의 공정이 있습니다.

1) vapor prime

친수성 표면인 wafer에 소수성 물질인 pr을 도포하기 위해 hmds라는 소수성 물질을 증기를 사용하여 도포합니다.

2) spin coat

웨이퍼를 빠르게 회전시켜 pr를 웨이퍼 위에 균일하게 도포합니다.

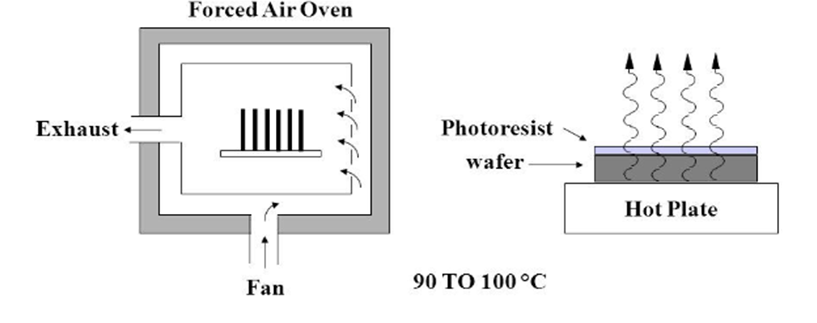

3) soft bake

pr이 액상 형태이므로 90~100도 사이의 온도로 구워서 pr내부에 있는 솔벤트를 제거하는 과정입니다. 솔벤트가 제거된 PR은 단단해집니다.

4) alignment&exposure

기판에 구성해 놓은 회로와 mask의 패턴을 정확하게 맞춥니다. 높은 에너지를 가진 빛을 조사하여 웨이퍼에 패턴을 그려 넣는 과정입니다. 회로 패턴이 그려져 있는 마스크에 빛을 쪼이면 마스크 패턴에 따라 통과된 빛만이 웨이퍼에 도달합니다. 빛을 받은 웨이퍼 위의 pr은 화학 반응을 일으키고 특성이 변하게 됩니다.

5) post expose bake

노광후 현상에 pr을 가열 건조하는 과정입니다. 노광 시 standing wave로 인해 울퉁불퉁한 표면이 생기게 됩니다. baking을 통해 표면을 매끄럽게 만들어 줄 수 있습니다.

6) develop

현상액을 이용하여 노광 후 필요 없는 부분을 제거하는 과정입니다.

7) hard baking

hard baking은 후속 공정으로 etching을 할 때 진행합니다. 잔여 solvent를 제거하여 pr을 건조하고 기판과 pr의 접착도를 증가시키는 역할을 합니다. hard baking공정은 lift off공정시는 사용하지 않기 때문에 선택적이라고 할 수 있습니다.

8) inspection

마지막으로 검사를 진행한 후 pr이 알맞게 도포돼 있으면 etching은 공정을 진행하게 됩니다. 만약 align이나 pr이 원하는 대로 도포되어 있지 않으면 pr을 모두 제거한 후 다시 재공정을 하게 됩니다. photo공정은 다른 공정과는 다르게 공정을 잘 못 하더라도 다시 pr을 지운 후 재공정을 할 수 있다는 장점이 있습니다.

resoulution

분해능은 얼마만큼 작은 패턴을 구현할 수 있는지를 나타내는 것으로 해상도를 결정 짓습니다. 보통 R로 표현하는데 이 값이 낮을수록 해상도가 좋다는 것을 의미합니다.

wavelength줄이기

파장은 회절, 주파수와 반비례 관계입니다. 광원에서 나오는 빛의 파장이 작을수록, 주파수가 클수록 해상도가 작아집니다.

NA높이기

아래위로 초점이 어느정도 일정한 유효거리가 길어야 유리합니다. 그러나 NA가 작을수록 DOF는 커집니다. 따라서 DOF와 해상도는 trade-off관계에 있으므로 서로 타협해 적정값을 찾아내야 합니다.

DOF(초점 깊이)

광학계에서 허용하는 초점의 범위입니다. resolution과 DOF는 trade-off 관계입니다.

PSM

위상 간섭을 통해서 파장을 짧게 만들어 미세한 패턴을 새길 수 있도록 합니다.

OPC

빛을 쏘면 마스크의 모양 그대로 웨이퍼에 패턴이 생기지 않습니다. 그래서 미리 마스크에 보완을 해서 웨이퍼상에 원하는 패턴이 나올 수 있도록 합니다.

multi patterning

반도체의 미세화 때문에 단일 패터닝으로는 포토 공정의 분해능의 한계로 공정 시 피치 사이에 빈 공간이 존재합니다. 멀티 패터닝 기술로 패턴의 밀도를 높일 수 있습니다. 기본적으로 패터닝을 두 번 하는 방식을 DPT라고 합니다. DPT에는 3가지 기법이 있습니다.

LLE기법 : 노광만 두 번 하는 기법

장점 : 적은 공정 스템, 낮은 공정 비용, 높은 해상도

단점 : 두번째 패터닝 시 첫번째 패턴에 화학적 처리 필요, 패턴 정렬도가 좋지 않음

LELE기법 : 하드마스크 막질을 이용해 노광 두번과 식각 두번하는 기법

장점 : 새로운 기법이 필요없음, 직관적 공정, 높은 해상도

단점 : 낮은 생산성, 패턴 정렬도가 좋지 않음

SADPT기법 : 스페이서를 이용해 etch back공정으로 패턴을 만드는 기법

장점 : 포토공정 필요횟수 1회, 높은 패턴 정렬도

단점 : 공정 스텝 증가, 공정 비용 증가, 필요한 여러 공정이 모두 최적화 되어야 함

주로 LLE와 LELE는 불균일한 패턴 형성에, SADPT는 균일한 패턴 형성에 사용됩니다.

EUV와 비교했을 때, EUV가 1번 패턴을 새길 때 여러 번 새겨야 합니다.

패턴의 모양도 EUV보다 부정확하게 나옵니다.

euv

euv란 반도체를 만드는데 있어 중요한 과정인 포토공정에서 극자외선 파장의 광원을 사용하는 리소그래피 기술 또는 이를 활용한 제조공정을 말합니다. 반도체 칩 제조 분야에선 웨이퍼 위에 극도로 미세한 회로를 새겨 넣는 것이 필수입니다. 그래야 트랜지스터와 콘덴서 등 소자들을 더 많이 집적하고, 성능과 효율을 높일 수 있기 때문입니다. euv광원은 기존 공정에 적용중인 불화 아르곤 광원보다 파장이 훨씬 짧습니다. 그래서 더 미세하게 패턴을 새길 수 있습니다.

LPP

특정 물질에 강한 레이저광을 집광하여 플라즈마를 만듭니다.

DPP

전극 간에 대 전류 펄스를 흘려 플라즈마를 만듭니다.

EUV 광원은 에너지가 커서 공기에서도 빛이 흡수됩니다. 그래서 진공 상태에서 반사를 이용해 빛을 쏩니다. 총 6개의 거울을 통해서 빛을 반사시키고, 마스크를 통해서 웨이퍼 위에 패턴을 새깁니다.

'IT기술' 카테고리의 다른 글

| physical verification 하는법 & 주의점. 반도체 backend 설계 (0) | 2023.03.05 |

|---|---|

| 반도체 SETUP HOLD timing구하는 법 (0) | 2023.03.05 |

| package에 사용하는 bump, innovus 커맨드. 반도체 backend 엔지니어 (0) | 2023.03.01 |

| 반도체 소자들 bjt, mosfet, cmos, latch up, fd-soi. 반도체 기본 지식 2탄 (0) | 2023.02.26 |

| 반도체 역사, energy band gap, pn junction. 반도체 기본 지식 1탄 (0) | 2023.02.25 |